# GreenLine<sup>™</sup> Compact Power Factor Controller: Innovative Circuit for Cost Effective Solutions

The MC33260 is a controller for Power Factor Correction preconverters meeting international standard requirements in electronic ballast and off–line power conversion applications. Designed to drive a free frequency discontinuous mode, it can also be synchronized and in any case, it features very effective protections that ensure a safe and reliable operation.

This circuit is also optimized to offer extremely compact and cost effective PFC solutions. While it requires a minimum number of external components, the MC33260 can control the follower boost operation that is an innovative mode allowing a drastic size reduction of both the inductor and the power switch. Ultimately, the solution system cost is significantly lowered.

Also able to function in a traditional way (constant output voltage regulation level), any intermediary solutions can be easily implemented. This flexibility makes it ideal to optimally cope with a wide range of applications.

## **General Features**

- Standard Constant Output Voltage or "Follower Boost" Mode

- Switch Mode Operation: Voltage Mode

- Latching PWM for Cycle-by-Cycle On-Time Control

- Constant On-Time Operation That Saves the Use of an Extra Multiplier

- Totem Pole Output Gate Drive

- Undervoltage Lockout with Hysteresis

- Low Start–Up and Operating Current

- Improved Regulation Block Dynamic Behavior

- Synchronization Capability

- Internally Trimmed Reference Current Source

## **Safety Features**

- Overvoltage Protection: Output Overvoltage Detection

- Undervoltage Protection: Protection Against Open Loop

- Effective Zero Current Detection

- Accurate and Adjustable Maximum On-Time Limitation

- Overcurrent Protection

- ESD Protection on Each Pin

Greenline is a trademark of Motorola, Inc.

# MC33260

# POWER FACTOR CONTROLLER

SEMICONDUCTOR TECHNICAL DATA

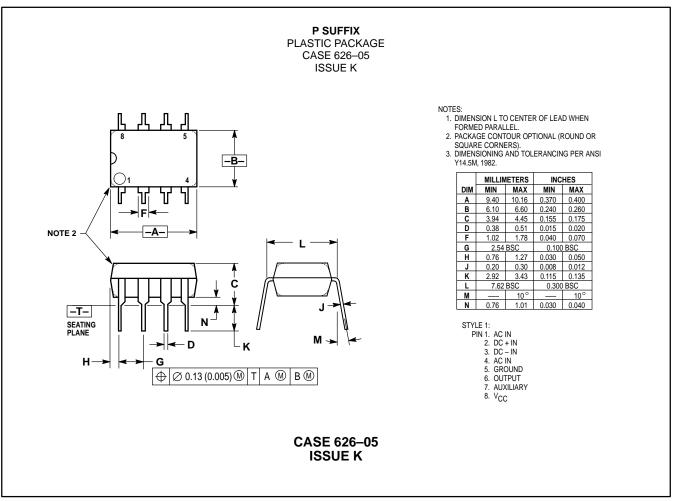

P SUFFIX PLASTIC PACKAGE CASE 626–05

# **ORDERING INFORMATION**

| Device   | Tested Operating<br>Temperature Range | Package       |  |  |

|----------|---------------------------------------|---------------|--|--|

| MC33260P | –40° to +105°C                        | Plastic DIP-8 |  |  |

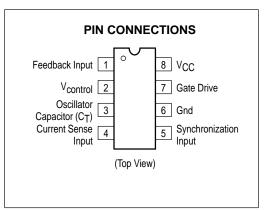

BLOCK DIAGRAM

# MAXIMUM RATINGS

| Rating                                                                                                                                                            | Pin # | Symbol                                         | Value       | Unit       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------------------------------|-------------|------------|

| Gate Drive Current (Pin 7)*<br>Source<br>Sink                                                                                                                     | 7     | l <sub>O(Source)</sub><br>l <sub>O(Sink)</sub> | 500<br>500  | mA         |

| V <sub>CC</sub> (Pin 8) Maximum Voltage                                                                                                                           | 8     | (Vcc) <sub>max</sub>                           | 16          | V          |

| Input Voltage                                                                                                                                                     |       | V <sub>in</sub>                                | -0.3 to +10 | V          |

| Power Dissipation and Thermal Characteristics<br>P Suffix, DIP Package<br>Maximum Power Dissipation @ T <sub>A</sub> = 85°C<br>Thermal Resistance Junction to Air |       | PD<br>R <sub>θ</sub> JA                        | 600<br>100  | mW<br>°C/W |

| Operating Junction Temperature                                                                                                                                    |       | ТJ                                             | 150         | °C         |

| Operating Ambient Temperature                                                                                                                                     |       | Т <sub>А</sub>                                 | -40 to +105 | °C         |

\*The maximum package power dissipation must be observed.

**ELECTRICAL CHARACTERISTICS** ( $V_{CC}$  = 13 V,  $T_J$  = 25°C for typical values,  $T_J$  = -40 to 105°C for min/max values unless otherwise noted.)

| Characteristic                                                                                                     | Pin # | Symbol                                 | Min     | Тур      | Max      | Unit    |

|--------------------------------------------------------------------------------------------------------------------|-------|----------------------------------------|---------|----------|----------|---------|

| GATE DRIVE SECTION                                                                                                 |       |                                        |         |          | •        |         |

| Gate Drive Resistor<br>Source Resistor @ I <sub>pin7</sub> = 100 mA<br>Sink Resistor @ I <sub>pin7</sub> = 100 mA  | 7     | R <sub>OL</sub><br>ROH                 | 10<br>5 | 20<br>10 | 35<br>25 | Ω       |

| Gate Drive Voltage Rise Time (From 3 V Up to 9 V) (Note 1)                                                         | 7     | tr                                     | _       | 50       | —        | ns      |

| Output Voltage Falling Time (From 9 V Down to 3 V) (Note 1)                                                        | 7     | t <sub>f</sub>                         | _       | 50       | —        | ns      |

| OSCILLATOR SECTION                                                                                                 |       |                                        |         |          |          |         |

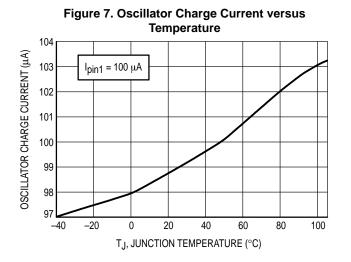

| Maximum Oscillator Swing                                                                                           | 3     | ΔV <sub>T</sub>                        | 1.4     | 1.5      | 1.6      | V       |

| Charge Current @ I <sub>pin1</sub> = 100 μA                                                                        | 3     | Icharge                                | 87.5    | 100      | 112.5    | μΑ      |

| Charge Current @ I <sub>pin1</sub> = 200 μA                                                                        | 3     | Icharge                                | 350     | 400      | 450      | μA      |

| Ratio Multiplier Gain Over Maximum Swing @ $I_{pin1}\text{=}100\mu\text{A}$                                        | 3     | K <sub>osc</sub>                       | 5600    | 6400     | 7200     | 1/(V.A) |

| Ratio Multiplier Gain Over Maximum Swing @ $I_{pin1} \mbox{=} 200  \mu \mbox{A}$                                   | 3     | K <sub>osc</sub>                       | 5600    | 6400     | 7200     | 1/(V.A) |

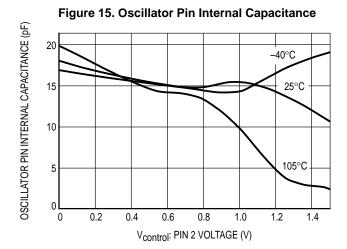

| Average Internal Pin 3 Capacitance Over Oscillator Maximum Swing ( $V_{pin3}$ Varying From 0 Up to 1.5 V) (Note 2) | 3     | C <sub>int</sub>                       | 10      | 15       | 20       | pF      |

| Discharge Time (C <sub>T</sub> = 1 nF)                                                                             | 3     | T <sub>disch</sub>                     | —       | 0.5      | 1        | μs      |

| REGULATION SECTION                                                                                                 |       |                                        |         |          | •        | •       |

| Regulation High Current Reference                                                                                  | 1     | I <sub>reg–H</sub>                     | 192     | 200      | 208      | μΑ      |

| Ratio (Regulation Low Current Reference)/Ireg-H                                                                    | 1     | I <sub>reg-L</sub> /I <sub>reg-H</sub> | 0.965   | 0.97     | 0.98     | —       |

| Pin 2 Impedance                                                                                                    | 1     | Z <sub>pin3</sub>                      | —       | 300      | —        | kΩ      |

| Pin 1 Clamp Voltage @ I <sub>pin1</sub> = 100 μA                                                                   | 1     | V <sub>pin1–100</sub>                  | 1.5     | 2.1      | 2.5      | V       |

| Pin 1 Clamp Voltage @ I <sub>pin1</sub> = 200 μA                                                                   | 1     | Vpin1–200                              | 2       | 2.6      | 3        | V       |

| CURRENT SENSE SECTION                                                                                              |       |                                        |         |          |          |         |

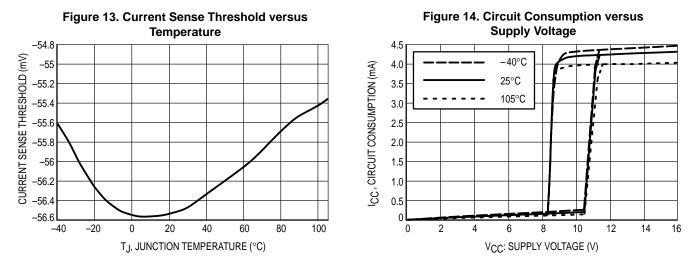

| Zero Current Detection Comparator Threshold                                                                        | 4     | VZCD-th                                | -90     | -60      | -30      | mV      |

| Negative Clamp Level (Ipin2 = -1 mA)                                                                               | 4     | Cl–neg                                 | —       | -0.7     | —        | V       |

| Bias Current @ V <sub>pin4</sub> = V <sub>ZCD-th</sub>                                                             | 4     | I <sub>b-cs</sub>                      | -0.2    | —        | —        | μΑ      |

| Propagation Delay ( $V_{pin4} > V_{ZCD-th}$ ) to Gate Drive High                                                   | 7     | TZCD                                   | —       | 500      | —        | ns      |

| Pin 4 Internal Current Source                                                                                      | 4     | IOCP                                   | 192     | 205      | 218      | μΑ      |

| Leading Edge Blanking Duration                                                                                     |       | τLEB                                   |         | 400      | —        | ns      |

| OverCurrent Protection Propagation Delay<br>(Pin 4 < V <sub>ZCD-th</sub> to Gate Drive Low)                        | 7     | TOCP                                   | 100     | 160      | 240      | ns      |

# **ELECTRICAL CHARACTERISTICS** (V<sub>CC</sub> = 13 V, T<sub>J</sub> = $25^{\circ}$ C for typical values, T<sub>J</sub> = -40 to $105^{\circ}$ C for min/max values unless otherwise noted.)

| Characteristic                                                                                                                     | Pin # | Symbol                     | Min  | Тур      | Max       | Unit |

|------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------|------|----------|-----------|------|

| SYNCHRONIZATION SECTION                                                                                                            |       |                            |      |          |           |      |

| Synchronization Threshold                                                                                                          | 5     | V <sub>sync-th</sub>       | 0.8  | 1        | 1.2       | V    |

| Negative Clamp Level (Ipin5 = -1 mA)                                                                                               | 5     | Cl–neg                     | _    | -0.7     | —         | V    |

| Minimum Off-Time                                                                                                                   | 7     | T <sub>off</sub>           | 1.5  | 2.1      | 2.7       | μs   |

| Minimum Required Synchronization Pulse Duration                                                                                    | 5     | T <sub>sync</sub>          | _    | —        | 0.5       | μs   |

| OVERVOLTAGE PROTECTION SECTION                                                                                                     |       |                            |      |          |           |      |

| OverVoltage Protection High Current Threshold<br>and I <sub>reg-H</sub> Difference                                                 | 1     | IOVP-H <sup>-I</sup> reg-H | 8    | 13       | 18        | μA   |

| OverVoltage Protection Low Current Threshold<br>and I <sub>reg-H</sub> Difference                                                  | 1     | IOVP-L <sup>-I</sup> reg-H | 0    | —        | —         | -    |

| Ratio (IOVP-H/IOVP-L)                                                                                                              | 1     | IOVP-H/IOVP-L              | 1.02 | -        | _         | -    |

| Propagation Delay (Ipin1 > 110% Iref to Gate Drive Low)                                                                            | 7     | T <sub>OVP</sub>           | _    | 500      | —         | ns   |

| UNDERVOLTAGE PROTECTION SECTION                                                                                                    |       |                            |      |          |           |      |

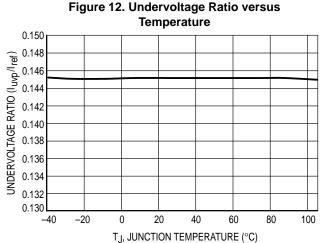

| Ratio (UnderVoltage Protection Current Threshold)/Ireg-H                                                                           | 1     | IUVP/Ireg-H                | 12   | 14       | 16        | %    |

| Propagation Delay (I <sub>pin1</sub> < 12% I <sub>ref</sub> to Gate Drive Low)                                                     | 7     | TUVP                       | _    | 500      | _         | ns   |

| THERMAL SHUTDOWN SECTION                                                                                                           |       |                            |      |          |           |      |

| Thermal Shutdown Threshold                                                                                                         | 7     | T <sub>stdwn</sub>         | —    | 150      | —         | °C   |

| Hysteresis                                                                                                                         | 7     | ΔT <sub>stdwn</sub>        | _    | 30       | _         | °C   |

| V <sub>CC</sub> UNDERVOLTAGE LOCKOUT SECTION                                                                                       |       |                            |      |          |           |      |

| Start–Up Threshold                                                                                                                 | 8     | V <sub>stup-th</sub>       | 9.7  | 11       | 12.3      | V    |

| Disable Voltage After Threshold Turn-On                                                                                            |       | V <sub>disable</sub>       | 7.4  | 8.5      | 9.6       | V    |

| TOTAL DEVICE                                                                                                                       |       | · · · · · ·                |      |          |           |      |

| Power Supply Current<br>Start–Up (V <sub>CC</sub> = 5 V with V <sub>CC</sub> Increasing)<br>Operating @ I <sub>pin1</sub> = 200 μA |       | Icc                        | _    | 0.1<br>4 | 0.25<br>8 | mA   |

NOTES: 1. 1 nF being connected between the pin 7 and ground.

2. Guaranteed by design.

3. No load is connected to the gate drive which is kept high during the test.

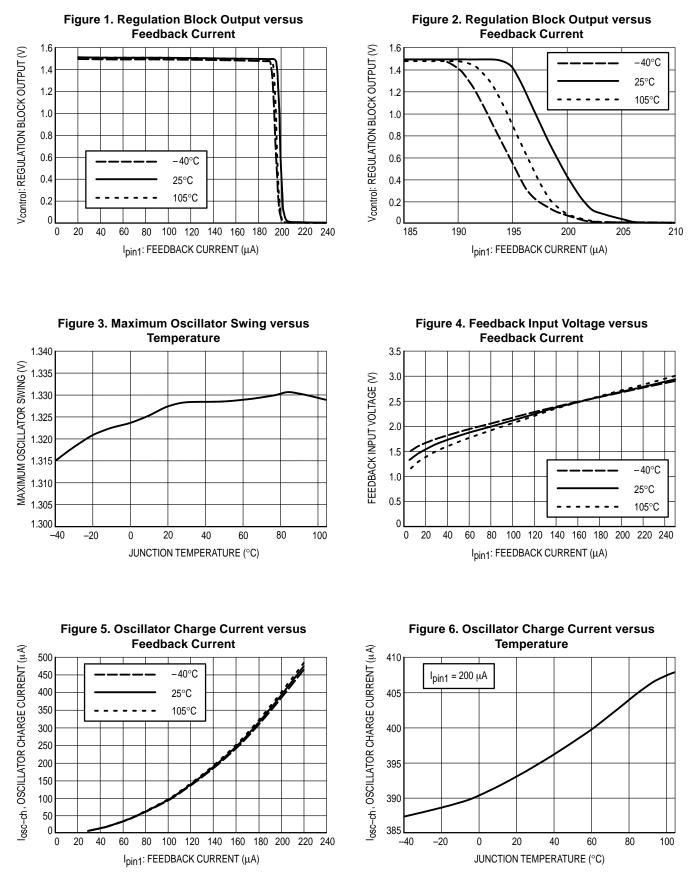

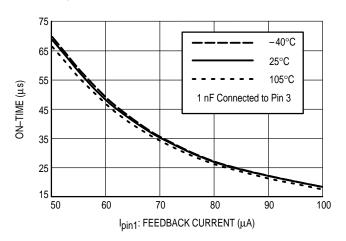

Figure 8. On-Time versus Feedback Current

Figure 9. On-Time versus Feedback Current

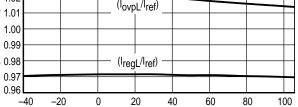

Figure 11. (IovpH/Iref), (IovpL/Iref), (IregL/Iref) versus Temperature 1.07 (lovpH /l ref.), (l ovpL /l ref.), (l regL/l ref.) 1.06 (IovpH/Iref) 1.05 1.04 1.03 1.02 (IovpL/Iref) 1.01

TJ, JUNCTION TEMPERATURE (°C)

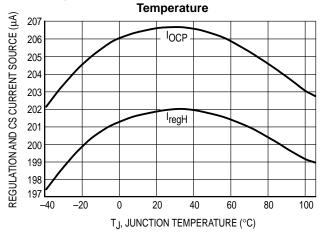

Figure 10. Internal Current Sources versus

Figure 12. Undervoltage Ratio versus

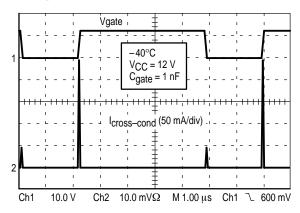

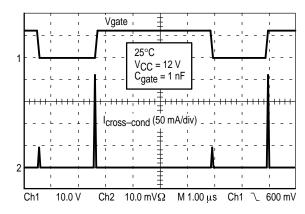

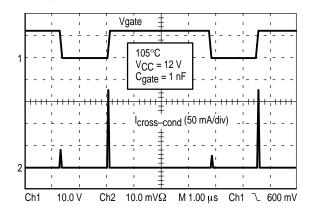

Figure 17. Gate Drive Cross Conduction

Figure 16. Gate Drive Cross Conduction

Figure 18. Gate Drive Cross Conduction

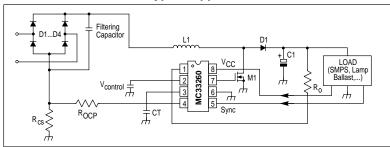

# **PIN FUNCTION DESCRIPTION**

| Pin No. | Function                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |

|---------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 1       | Feedback Input                            | This pin is designed to receive a current that is proportional to the preconverter output voltage. This information is used for both the regulation and the overvoltage and undervoltage protections. The current drawn by this pin is internally squared to be used as oscillator capacitor charge current.                                                                                                                                                             |  |  |  |  |  |  |  |  |

| 2       | V <sub>control</sub>                      | This pin makes available the regulation block output. The capacitor connected between this pin and ground, adjusts the control bandwidth. It is typically set below 20 Hz to obtain a nondistorted input current.                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |

| 3       | Oscillator Capacitor<br>(C <sub>T</sub> ) | The circuit uses an on-time control mode. This on-time is controlled by comparing the $C_T$ voltage to the V <sub>control</sub> voltage. $C_T$ is charged by the squared feedback current.                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |

| 4       | Zero Current<br>Detection Input           | This pin is designed to receive a negative voltage signal proportional to the current flowing through the inductor. This information is generally built using a sense resistor. The Zero Current Detection prevents any restart as long as the pin 4 voltage is below (–60 mV). This pin is also used to perform the peak current limitation. The overcurrent threshold is programmed by the resistor connected between the pin and the external current sense resistor. |  |  |  |  |  |  |  |  |

| 5       | Synchronization<br>Input                  | This pin is designed to receive a synchronization signal. For instance, it enables to synchronize the PFC preconverter to the associated SMPS. If not used, this pin must be grounded.                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |

| 6       | Ground                                    | This pin must be connected to the preregulator ground.                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |

| 7       | Gate Drive                                | The gate drive current capability is suited to drive an IGBT or a power MOSFET.                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

| 8       | VCC                                       | This pin is the positive supply of the IC. The circuit turns on when $V_{CC}$ becomes higher than 11 V, the operating range after start–up being 8.5 V up to 16 V.                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

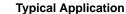

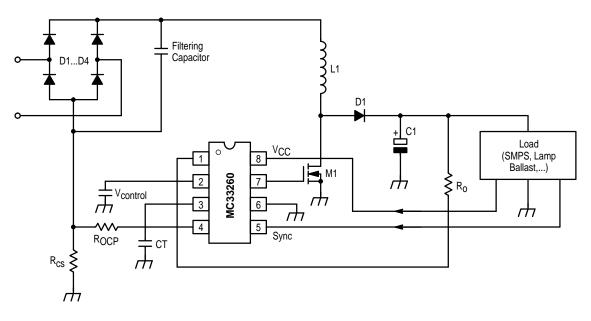

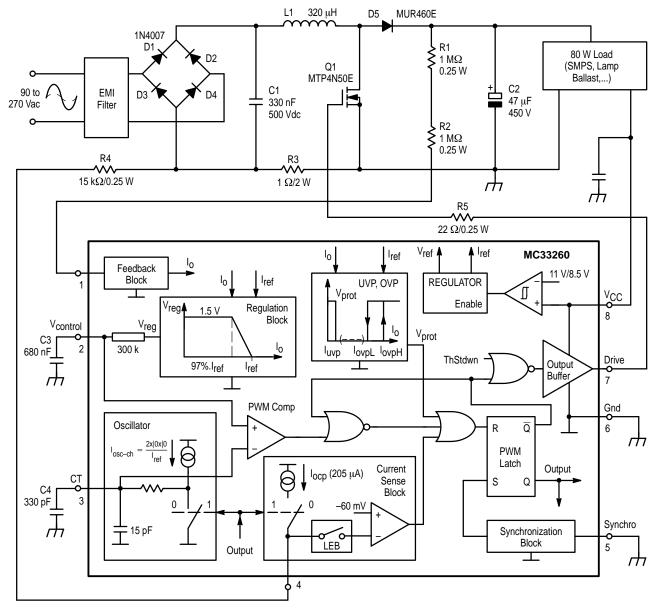

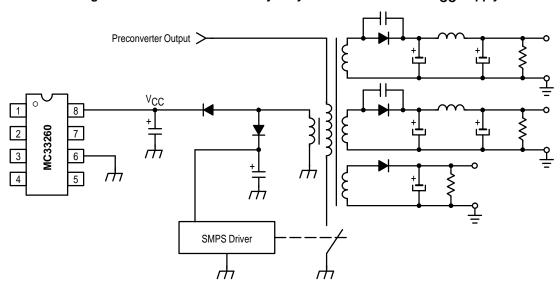

# **APPLICATION SCHEMATIC**

# FUNCTIONAL DESCRIPTION

### INTRODUCTION

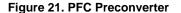

The need of meeting the requirements of legislation on line current harmonic content, results in an increasing demand for cost effective solutions to comply with the Power Factor regulations. This data sheet describes a monolithic controller specially designed for this purpose.

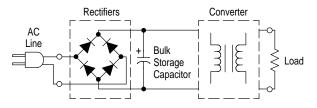

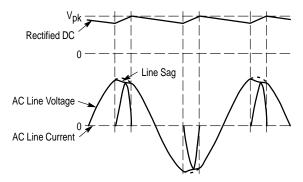

Most off-line appliances use a bridge rectifier associated to a huge bulk capacitor to derive raw dc voltage from the utility ac line.

#### Figure 19. Typical Circuit Without PFC

This technique results in a high harmonic content and in poor power factor ratios. In effect, the simple rectification technique draws power from the mains when the instantaneous ac voltage exceeds the capacitor voltage. This occurs near the line voltage peak and results in a high charge current spike. Consequently, a poor power factor (in the range of 0.5 - 0.7) is generated, resulting in an apparent input power that is much higher than the real power.

Active solutions are the most popular way to meet the legislation requirements. They consist of inserting a PFC pre-regulator between the rectifier bridge and the bulk capacitor. This interface is, in fact, a step-up SMPS that outputs a constant voltage while drawing a sinusoidal current from the line.

The MC33260 was developed to control an active solution with the goal of increasing its robustness while lowering its global cost.

#### **OPERATION DESCRIPTION**

The MC33260 is optimized to just as well drive a free running as a synchronized discontinuous voltage mode.

It also features valuable protections (overvoltage and undervoltage protection, overcurrent limitation, ...) that make the PFC preregulator very safe and reliable while requiring very few external components. In particular, it is able to safely face any uncontrolled direct charges of the output capacitor from the mains which occur when the output voltage is lower than the input voltage (start–up, overload, ...).

In addition to the low count of elements, the circuit can control an innovative mode named "Follower Boost" that permits to significantly reduce the size of the preconverter inductor and power MOSFET. With this technique, the output regulation level is not forced to a constant value, but can vary according to the a.c. line amplitude and to the power. The gap between the output voltage and the ac line is then lowered, what allows the preconverter inductor and power MOSFET size reduction. Finally, this method brings a significant cost reduction.

A description of the functional blocks is given below.

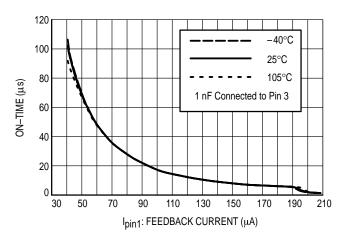

## **REGULATION SECTION**

Connecting a resistor between the output voltage to be regulated and the pin 1, a feedback current is obtained. Typically, this current is built by connecting a resistor between the output voltage and the pin 1. Its value is then given by the following equation:

$$I_{pin1} = \frac{V_0 - V_{pin1}}{R_0}$$

where:

Ro is the feedback resistor,

$V_{0}$  is the output voltage,

Vpin1 is the pin 1 clamp value.

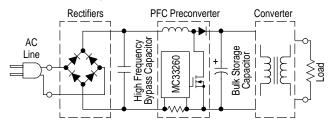

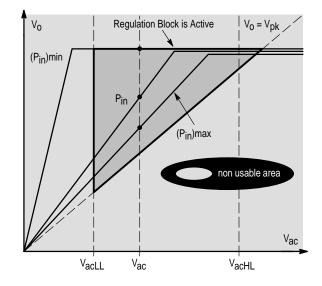

The feedback current is compared to the reference current so that the regulation block outputs a signal following the characteristic depicted in Figure 22. According to the power and the input voltage, the output voltage regulation level varies between two values  $(V_0)_{regL}$  and  $(V_0)_{regH}$  corresponding to the I<sub>regL</sub> and I<sub>regH</sub> levels.

#### **Figure 22. Regulation Characteristic**

The feedback resistor must be chosen so that the feedback current should equal the internal current source  $I_{regH}$  when the output voltage exceeds the chosen upper regulation voltage [( $V_0$ )<sub>regH</sub>]. Consequently:

$$R_{o} = \frac{(V_{o})_{regH} - V_{pin1}}{I_{regH}}$$

In practice, V<sub>pin1</sub> is small compared to (V<sub>0</sub>)<sub>regH</sub> and this equation can be simplified as follows (I<sub>regH</sub> being also replaced by its typical value 200  $\mu$ A):

$$R_{o} \approx 5 \times (V_{o})_{reaH} < k\Omega > 0$$

The regulation block output is connected to the pin 2 through a 300 k $\Omega$  resistor. The pin 2 voltage (V<sub>control</sub>) is compared to the oscillator sawtooth for PWM control.

An external capacitor must be connected between pin 2 and ground, for external loop compensation. The bandwidth is typically set below 20 Hz so that the regulation block output should be relatively constant over a given ac line cycle. This integration that results in a constant on-time over the ac line period, prevents the mains frequency output ripple from distorting the ac line current.

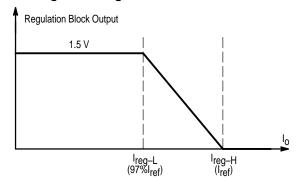

## **OSCILLATOR SECTION**

The oscillator consists of three phases:

- Charge Phase: The oscillator capacitor voltage grows up linearly from its bottom value (ground) until it exceeds V<sub>control</sub> (regulation block output voltage). At that moment, the PWM latch output gets low and the oscillator discharge sequence is set.

- Discharge Phase: The oscillator capacitor is abruptly discharged down to its valley value (0 V).

- Waiting Phase: At the end of the discharge sequence, the oscillator voltage is maintained in a low state until the PWM latch is set again.

Figure 23. Oscillator

The oscillator charge current is dependent on the feedback current ( $I_0$ ). In effect

$$I_{charge} = 2 \times \frac{I_o^2}{I_{ref}}$$

where:

Icharge is the oscillator charge current,

Io is the feedback current (drawn by pin 1),

$I_{ref}$  is the internal reference current (200  $\mu$ A).

So, the oscillator charge current is linked to the output voltage level as follows:

$$I_{charge} = \frac{2 \times \left\langle V_{o} - V_{pin1} \right\rangle^{2}}{R_{o}^{2} \times I_{ref}}$$

where:

$V_0 \text{ is the output voltage,} \\ R_0 \text{ is the feedback resistor,} \\ V_{\text{pin1}} \text{ is the pin 1 clamp voltage.}$

In practice,  $V_{pin1}$  that is in the range of 2.5 V, is very small compared to  $V_0$ . The equation can then be simplified by neglecting  $V_{pin1}$ :

$$I_{\text{charge}} \approx \frac{2 \times V_0^2}{R_0^2 \times I_{\text{ref}}}$$

It must be noticed that the oscillator terminal (pin 3) has an internal capacitance ( $C_{int}$ ) that varies versus the pin 3 voltage. Over the oscillator swing, its average value typically equals 15 pF (min 10 pF, max 20 pF).

The total oscillator capacitor is then the sum of the internal and external capacitors.

$$C_{pin3} = C_T + C_{int}$$

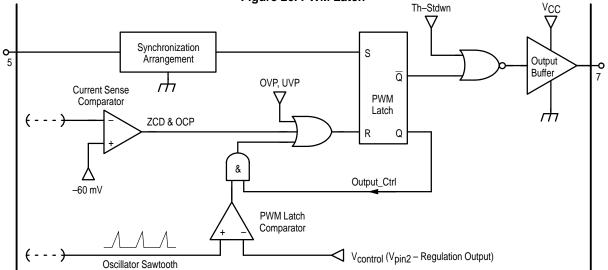

## **PWM LATCH SECTION**

The MC33260 operates in voltage mode: the regulation block output ( $V_{control}$  – pin 2 voltage) is compared to the oscillator sawtooth so that the gate drive signal (pin 7) is high until the oscillator ramp exceeds  $V_{control}$ .

The on-time is then given by the following equation:

$$t_{on} = \frac{C_{pin3} \times V_{control}}{I_{ch}}$$

where:

ton is the on-time,

C<sub>pin3</sub> is the total oscillator capacitor (sum of the internal and external capacitor),

$I_{charge}$  is the oscillator charge current (pin 3 current),  $V_{control}$  is the pin 2 voltage (regulation block output).

Consequently, replacing  $I_{charge}$  by the expression given in the Oscillator Section:

$$t_{on} = \frac{R_o^2 \times I_{ref} \times C_{pin3} \times V_{control}}{2 \times V_o^2}$$

One can notice that the on-time depends on  $V_0$  (preconverter output voltage) and that the on-time is maximum when Vcontrol is maximum (1.5 V typically).

At a given  $V_0$ , the maximum on-time is then expressed by the following equation:

$$\langle t_{on} \rangle max = \frac{C_{pin3} \times R_{o}^{2} \times I_{ref} \times \left\langle V_{control} \right\rangle_{max}}{2 \times V_{o}^{2}}$$

This equation can be simplified replacing

{2 / [(V<sub>control</sub>)<sub>max</sub> \* I<sub>ref</sub>]} by K<sub>osc</sub>

Refer to **Electrical Characteristics**, **Oscillator Section**. Then:

$$\langle t_{on} \rangle$$

max =  $\frac{C_{pin3} \times R_o^2}{K_{osc} \times V_o^2}$

This equation shows that the maximum on-time is inversely proportional to the squared output voltage. This property is used for follower boost operation (refer to **Follower Boost** section).

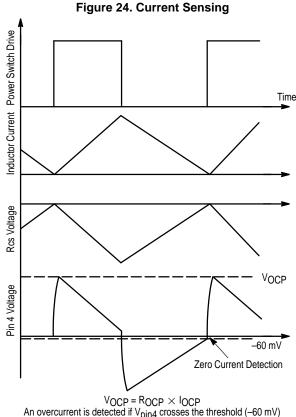

#### **CURRENT SENSE BLOCK**

The inductor current is converted into a voltage by inserting a ground referenced resistor ( $R_{CS}$ ) in series with the input diodes bridge (and the input filtering capacitor). Therefore a negative voltage proportional to the inductor current is built:

$$V_{cs} = - \langle R_{cs} \times I_L \rangle$$

where:

IL is the inductor current,

R<sub>cs</sub> is the current sense resistor,

V<sub>CS</sub> is the measured R<sub>CS</sub> voltage.

An overcurrent is detected if Vpin4 crosses the threshold (–60 mV) during the Power Switch on state

The negative signal V<sub>CS</sub> is applied to the current sense through a resistor ROCP. The pin is internally protected by a negative clamp (-0.7 V) that prevents substrate injection.

As long as the pin 4 voltage is lower than (-60 mV), the Current Sense comparator resets the PWM latch to force the gate drive signal low state. In that condition, the power MOSFET cannot be on.

During the on-time, the pin 4 information is used for the overcurrent limitation while it serves the zero current detection during the off time.

#### **Zero Current Detection**

The Zero Current Detection function guarantees that the MOSFET cannot turn on as long as the inductor current hasn't reached zero (discontinuous mode).

The pin 4 voltage is simply compared to the (-60 mV) threshold so that as long as V<sub>CS</sub> is lower than this threshold, the circuit gate drive signal is kept in low state. Consequently, no power MOSFET turn on is possible until the inductor current is measured as smaller than (60 mV/R<sub>CS</sub>) that is, the inductor current nearly equals zero.

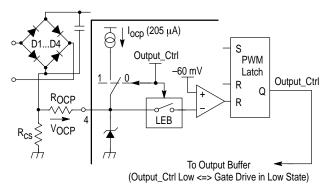

#### Figure 25. Current Sense Block

#### **Overcurrent Protection**

During the power switch conduction (i.e. when the Gate Drive pin voltage is high), a current source is applied to the pin 4. A voltage drop VOCP is then generated across the resistor ROCP that is connected between the sense resistor and the Current Sense pin (refer to Figure 25). So, instead of  $V_{CS}$ , the sum ( $V_{CS}$  +  $V_{OCP}$ ) is compared to (-60 mV) and the maximum permissible current is the solution of the following equation:

$$-\langle R_{cs} \times Ipk_{max} \rangle + V_{OCP} = -60 \text{ mV}$$

where:

Ipkmax is maximum allowed current, R<sub>CS</sub> is the sensing resistor.

The overcurrent threshold is then:

$$lpk_{max} = \frac{\left\langle R_{OCP} \times I_{OCP} \right\rangle + 60 \times 10^{-3}}{R_{cs}}$$

where:

ROCP is the resistor connected between the pin and the sensing resistor (R<sub>CS</sub>),

IOCP is the current supplied by the Current Sense pin when the gate drive signal is high (power switch conduction phase). IOCP equals 205 µA typically.

Practically, the VOCP offset is high compared to 60 mV and the precedent equation can be simplified. The maximum current is then given by the following equation:

$$lpk_{max} \approx \frac{R_{OCP}^{< k\Omega>}}{R_{cs} < \Omega>} \times 0.205 < A>$$

Consequently, the ROCP resistor can program the OCP level whatever the R<sub>CS</sub> value is. This gives a high freedom in the choice of R<sub>CS</sub>. In particular, the inrush resistor can be utilized.

Figure 26. PWM Latch

A LEB (Leading Edge Blanking) has been implemented. This circuitry disconnects the Current Sense comparator from pin 4 and disables it during the 400 first ns of the power switch conduction. This prevents the block from reacting on the current spikes that generally occur at power switch turn on. Consequently, proper operation does not require any filtering capacitor on pin 4.

## PROTECTIONS

OCP (Overcurrent Protection) Refer to Current Sense Block.

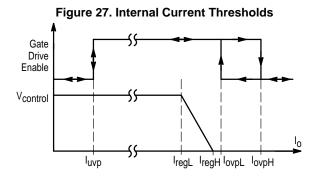

# **OVP (Overvoltage Protection)**

The feedback current  $(I_0)$  is compared to a threshold current  $(I_{OVPH})$ . If it exceeds this value, the gate drive signal is maintained low until this current gets lower than a second level  $(I_{OVPL})$ .

So, the OVP upper threshold is:

$$V_{ovpH} = V_{pin1} + (R_o \times I_{ovpH})$$

where:

$\mathsf{R}_{\mathsf{O}}$  is the feedback resistor that is connected between pin 1 and the output voltage,

$I_{OVP-H}$  is the internal upper OVP current threshold,  $V_{pin1}$  is the pin 1 clamp voltage.

Practically,  $V_{pin1}$  that is in the range of 2.5 V, can be neglected. The equation can then be simplified:

$$V_{ovpH} = R_o < M\Omega > \times I_{ovpH} < \mu A > < V >$$

On the other hand, the OVP low threshold is:

$$V_{ovpL} = V_{pin1} + \left(R_{o} \times I_{ovpL}\right)$$

where  $I_{OVP-L}$  is the internal low OVP current threshold. Consequently,  $V_{\text{pin1}}$  being neglected:

$$V_{ovpL} = R_o < M\Omega > \times I_{ovpL} < \mu A > < V >$$

The OVP hysteresis prevents erratic behavior.

$I_{OVPL}$  is guaranteed to be higher than IregH (refer to parameters specification). This ensures that the OVP function doesn't interfere with the regulation one.

# **UVP (Undervoltage Protection)**

This function detects when the feedback current is lower than 14% of  $I_{\text{ref}}$ . In this case, the PWM latch is reset and the power switch is kept off.

- This protection is useful to:

- Protect the preregulator from working in too low mains conditions.

- To detect the feedback current absence (in case of a nonproper connection for instance).

The UVP threshold is:

$$V_{uvp} \approx V_{pin1} + \left(R_0 < M\Omega > \times I_{uvp} < \mu A > \right) (V)$$

Practically (Vpin1 being neglected),

$V_{uvp} = R_0 < M\Omega > \times I_{uvp} < \mu A > < V >$

# **Maximum On–Time Limitation**

As explained in **PWM Latch**, the maximum on-time is accurately controlled.

# **Pin Protection**

All the pins are ESD protected.

In particular, a 11 V zener diode is internally connected between the terminal and ground on the following pins: Feedback,  $V_{control}$ , Oscillator, Current Sense, and Synchronization.

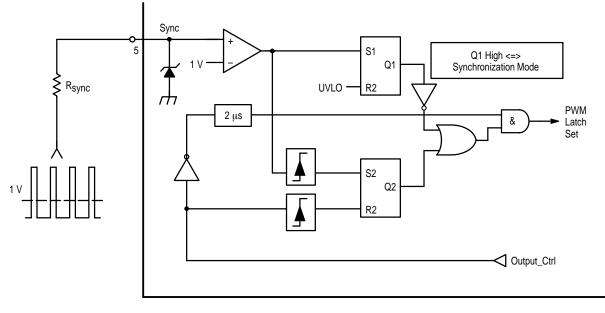

## Figure 28. Synchronization arrangement

## SYNCHRONIZATION BLOCK

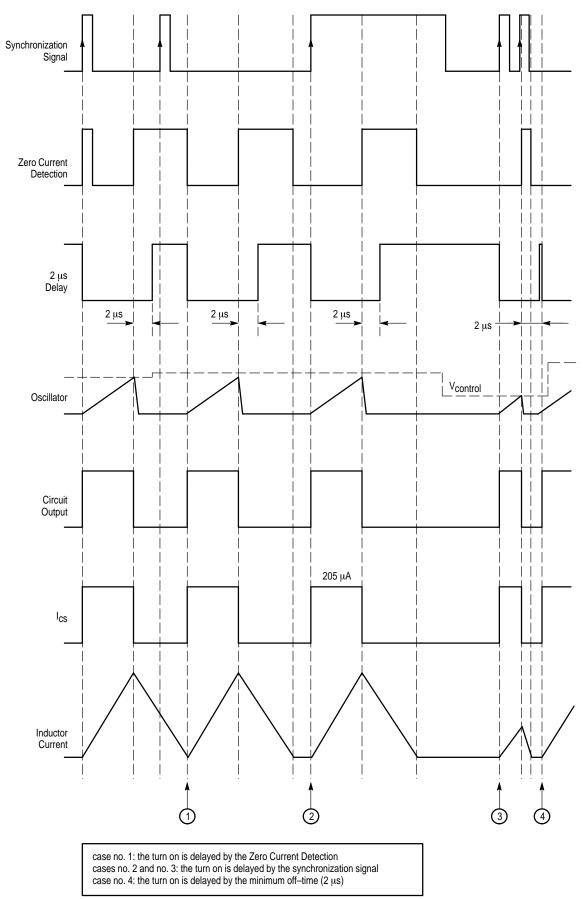

The MC33260 features two modes of operation:

- Free Running Discontinuous Mode: The power switch is turned on as soon as there is no current left in the inductor (Zero Current Detection). This mode is simply obtained by grounding the synchronization terminal (pin 5).

- Synchronization Mode: This mode is set as soon as a signal crossing the 1 V threshold, is applied to the pin 5. In this case, operation in free running can only be recovered after a new circuit start-up. In this mode, the power switch cannot turn on before the two following conditions are fulfilled.

- Still, the zero current must have been detected.

- The precedent turn on must have been followed by (at least) one synchronization raising edge crossing the 1 V threshold.

In other words, the synchronization acts to prolong the power switch off time.

Consequently, a proper synchronized operation requires that the current cycle (on–time + inductor demagnetization) is shorter than the synchronization period. Practically, the inductor must be chosen accordingly. Otherwise, the system will keep working in free running discontinuous mode. Figure 33 illustrates this behavior.

It must be noticed that whatever the mode is, a 2  $\mu$ s minimum off-time is forced. This delay limits the switching frequency in light load conditions.

## **OUTPUT SECTION**

The output stage contains a totem pole optimized to minimize the cross conduction current during high speed operation. The gate drive is kept in a sinking mode whenever the Undervoltage Lockout is active. The rise and fall times have been controlled to typically equal 50 ns while loaded by 1 nF.

#### **REFERENCE SECTION**

An internal reference current source ( $I_{ref}$ ) is trimmed to be ±4% accurate over the temperature range (the typical value is 200 µA).  $I_{ref}$  is the reference used for the regulation ( $I_{regH} = I_{ref}$ ).

#### UNDERVOLTAGE LOCKOUT SECTION

An Undervoltage Lockout comparator has been implemented to guarantee that the integrated circuit is operating only if its supply voltage ( $V_{CC}$ ) is high enough to enable a proper working. The UVLO comparator monitors the pin 8 voltage and when it exceeds 11 V, the device gets active. To prevent erratic operation as the threshold is crossed, 2.5 V of hysteresis is provided.

The circuit off state consumption is very low: in the range of 100  $\mu$ A @ V<sub>CC</sub> = 5 V. This consumption varies versus V<sub>CC</sub> as the circuit presents a resistive load in this mode.

## THERMAL SHUTDOWN

An internal thermal circuitry is provided to disable the circuit gate drive and then to prevent it from oscillating, if the junction temperature exceeds 150°C typically.

The output stage is again enabled when the temperature drops below 120°C typically (30°C hysteresis).

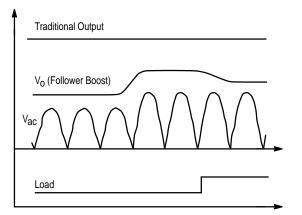

## FOLLOWER BOOST

Traditional PFC preconverters provide the load with a fixed and regulated voltage that generally equals 230 V or 400 V according to the mains type (U.S., European, or universal).

In the "Follower Boost" operation, the preconverter output regulation level is not fixed but varies linearly versus the ac line amplitude at a given input power.

## Figure 29. Follower Boost Characteristics

Figure 30. Off-Time Duration Increase

the power switch is on

the power switch is off

#### **Follower Boost Implementation**

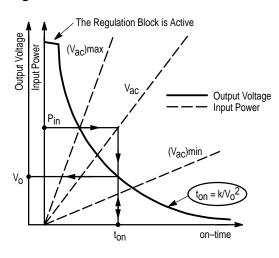

In the MC33260, the on-time is differently controlled according to the feedback current level. Two areas can be defined:

- When the feedback current is higher than I<sub>regL</sub> (refer to regulation section), the regulation block output (V<sub>control</sub>) is modulated to force the output voltage to a desired value.

- On the other hand, when the feedback current is lower than I<sub>regL</sub>, the regulation block output and therefore, the on-time are maximum. As explained in **PWM Latch** Section, the on-time is then inversely proportional to the output voltage square. The Follower Boost is active in these conditions in which the on-time is simply limited by the output voltage level. Note: In this equation, the feedback pin voltage (V<sub>pin1</sub>) is neglected compared to the output voltage (refer to the **PWM Latch Section**).

$$t_{on} = \langle t_{on} \rangle max = \frac{C_{pin3} \times R_o^2}{K_{osc} \times V_o^2}$$

where:

$C_{pin3}$  is the total oscillator capacitor (sum of the internal and external capacitors –  $C_{int}$  +  $C_T$ ),

$K_{\mbox{\scriptsize OSC}}$  is the ratio (oscillator swing over oscillator gain),

V<sub>0</sub> is the output voltage,

R<sub>0</sub> is the feedback resistor.

On the other hand, the boost topology has its own rule that dictates the on-time necessary to deliver the required power:

$$t_{on} = \frac{4 \times L_p \times P_{in}}{V_{pk}^2}$$

where:

Vpk is the peak ac line voltage,

Lp is the inductor value,

Pin is the input power.

This technique aims at reducing the gap between the output and the input voltages to minimize the boost efficiency degradation.

## **Follower Boost Benefits**

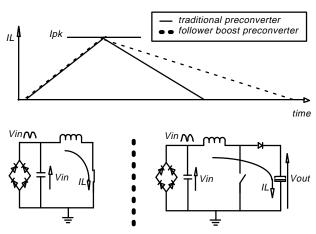

The boost presents two phases:

- The on-time during which the power switch is on. The inductor current grows up linearly according to a slope  $(V_{in}/L_p)$ , where  $V_{in}$  is the instantaneous input voltage and  $L_p$  the inductor value.

- The off-time during which the power switch is off. The inductor current decreases linearly according the slope  $(V_0 V_{in})/L_p$ , where  $V_0$  is the output voltage. This sequence that terminates when the current equals zero, has a duration that is inversely proportional to the gap between the output and input voltages. Consequently, the off-time duration becomes longer in follower boost.

Consequently, for a given peak inductor current, the longer the off time, the smaller power switch duty cycle and then its conduction dissipation. This is the first benefit of this technique: the MOSFET on-time losses are reduced.

The increase of the off time duration also results in a switching frequency diminution (for a given inductor value). Given that in practise, the boost inductor is selected big enough to limit the switching frequency down to an acceptable level, one can immediately see the second benefit of the follower boost: it allows the use of smaller, lighter and cheaper inductors compared to traditional systems.

Finally, this technique utilization brings a drastic system cost reduction by lowering the size and then the cost of both the inductor and the power switch. Combining the two equations, one can obtain the Follower Boost equation:

$$V_{0} = \frac{R_{0}}{2} \times \sqrt{\frac{C_{pin3}}{K_{osc} \times L_{p} \times P_{in}}} \times V_{pk}$$

Consequently, a linear dependency links the output voltage to the ac line amplitude at a given input power.

**Figure 31. Follower Boost Characteristics**

The behavior of the output voltage is depicted in Figures 31 and 32. In particular, Figure 31 illustrates how the output voltage converges to a stable equilibrium level. First, at a given ac line voltage, the on-time is dictated by the power demand. Then, the follower boost characteristic makes correspond one output voltage level to this on-time. Combining these two laws, it appears that the power level forces the output voltage.

One can notice that the system is fully stable:

- If an output voltage increase makes it move away from its equilibrium value, the on-time will immediately diminish according to the follower boost law. This will result in a delivered power decrease. Consequently, the supplied power being too low, the output voltage will decrease back,

- In the same way, if the output voltage decreases, more power will be transferred and then the output voltage will increase back.

Figure 32. Follower Boost Output Voltage

#### **Mode Selection**

The operation mode is simply selected by adjusting the oscillator capacitor value. As shown in Figure 32, the output voltage first has an increasing linear characteristic versus the ac line magnitude and then is clamped down to the regulation value. In the traditional mode, the linear area must be rejected. This is achieved by dimensioning the oscillator capacitor so that the boost can deliver the maximum power while the output voltage equals its regulation level and this, whatever the given input voltage. Practically, that means that whatever the power and input voltage conditions are, the follower boost would generate output voltages values higher than the regulation level, if there was no regulation block.

In other words, if  $(V_0)_{regL}$  is the low output regulation level:

$$\langle V_{o} \rangle_{regL} \leq \frac{R_{o}}{2} \times \sqrt{\frac{C_{T} + C_{int}}{\kappa_{osc} \times L_{p} \times \langle P_{in} \rangle max}} \times V_{pk}$$

Consequently,

$$C_{T} \geq C_{int} + \frac{4 \times K_{osc} \times L_{p} \times \left\langle \mathsf{P}_{in} \right\rangle max \times \left\langle \mathsf{V}_{o} \right\rangle_{regL}^{2}}{R_{o}^{2} \times V_{pk}^{2}}$$

Using  $I_{regL}$  (regulation block current reference), this equation can be simplified as follows:

$$C_{T} \geq C_{int} + \frac{4 \times K_{osc} \times L_{p} \times \left\langle \mathsf{P}_{in} \right\rangle_{max} \times \mathsf{I}_{regL}^{2}}{\mathsf{V}_{pk}^{2}}$$

In the Follower Boost case, the oscillator capacitor must be chosen so that the wished characteristics are obtained.

Consequently, the simple choice of the oscillator capacitor enables the mode selection.

# Figure 33. Typical Waveforms

# MAIN DESIGN EQUATIONS (Note 1)

| rms Input Current (I <sub>ac</sub> ) $I_{ac} = \frac{P_{o}}{\eta \times V_{ac}}$                                                                                                                                                                                                                                                                                   | $\eta$ (preconverter efficiency) is generally in the range of 90 – 95%.                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Maximum Inductor Peak Current ((I <sub>pk</sub> )max):<br>$(I_{pk})max = \frac{2 \times \sqrt{2} \times (P_0)max}{\eta \times V_{acLL}}$                                                                                                                                                                                                                           | (I <sub>pk</sub> )max is the maximum inductor current.                                                                                                                                                 |

| Output Voltage Peak to Peak 100Hz (120Hz) Ripple (( $\Delta$ Vo)pk–pk):<br>$(\Delta V_0)_{pk-pk} = \frac{P_0}{2\pi \times f_{ac} \times C_0 \times V_0}$                                                                                                                                                                                                           | f <sub>ac</sub> is the ac line frequency (50 or 60Hz)                                                                                                                                                  |

| Inductor Value (L <sub>p</sub> ):<br>$L_{p} = \frac{2 \times t \times \left(\frac{V_{o}}{\sqrt{2}} - V_{acLL}\right) \times V_{acLL}^{2}}{V_{o} \times V_{acLL} \times (I_{pk}) \max}$                                                                                                                                                                             | t is the maximum switching period.<br>(t=40μs) for universal mains operation and<br>(t=20μs) for narrow range are generally used.                                                                      |

| $\begin{split} \text{Maximum Power MOSFET Conduction Losses ((p_{ON})max):} \\ (P_{ON})  \text{max} &\approx \frac{1}{3} \times (\text{Rds}) \text{on} \times (I_{pk})  \text{max}^2 \times \left[1 - \frac{1.2 \times V_{acLL}}{V_0}\right] \end{split}$                                                                                                          | (Rds)on is the MOSFET drain source on–time resistor. In Follower Boost, the ratio ( $V_{acLL}/V_0$ ) is higher. The on–time MOSFET losses are then reduced                                             |

| Maximum Average Diode Current (I <sub>d</sub> ):<br>$(I_d) max = \frac{(P_0) max}{(V_0) min}$                                                                                                                                                                                                                                                                      | The Average Diode Current depends on the power and on the output voltage.                                                                                                                              |

| Current Sense Resistor Losses (pR <sub>CS</sub> ): $pR_{CS} = \frac{1}{6} \times (Rds) on \times (I_{pk})^2 max$                                                                                                                                                                                                                                                   | This formula indicates the required dissipation capability for $R_{CS}$ (current sense resistor).                                                                                                      |

| Over Current Protection Resistor (R <sub>OCP</sub> ):<br>$R_{OCP} \approx \frac{R_{CS} \times (I_{pk}) \max}{0.205} $ (kΩ)                                                                                                                                                                                                                                         | The overcurrent threshold is adjusted by $R_{OCP}$ at a given $R_{cs}$ . $R_{cs}$ can be a preconverter inrush resistor                                                                                |

| $ \begin{array}{l} \text{Oscillator External Capacitor Value (C_T):} \\ -\text{Traditional Operation} \\ C_T \geq C_{int} + \frac{2 \times K_{OSC} \times L_p \times (P_{in}) \max \times I_{regL}^2}{V_{ac}^2} \\ -\text{Follower Boost:} \\ V_0 = \frac{R_0}{2} \times \sqrt{\frac{C_T + C_{int}}{K_{OSC} \times L_p \times P_{in}}} \times V_{pk} \end{array} $ | The Follower Boost characteristic is adjusted by the C <sub>T</sub> choice.<br>The Traditional Mode is also selected by C <sub>T</sub> .<br>C <sub>int</sub> is the oscillator pin internal capacitor. |

| Feedback Resistor (R <sub>0</sub> ):<br>$R_{0} = \frac{(V_{0})_{reg} - V_{pin1}}{I_{regH}} \approx \frac{V_{0}}{200} $ (M\Omega) Note . 1. The preconverter design requires the following characteristics specification:                                                                                                                                           | The output voltage regulation level is adjusted by $R_{0}.$                                                                                                                                            |

Note . 1. The preconverter design requires the following characteristics specification:  $-(V_0)_{reg}$ : desired output voltage regulation level  $-(\Delta V_0)_{pk-pk}$ : admissible output peak to peak ripple voltage  $-P_0$ : desired output power  $-V_{ac}$ : ac rms operating line voltage  $-V_{acLL}$ : minimum ac rms operating line voltage

### Figure 34. 80 W Wide Mains Power Factor Corrector

L1: Coilcraft N2881 – A (primary: 62 turns of # 22 AWG – Secondary: 5 turns of # 22 AWG

Core: Coilcraft PT2510, EE 25

Gap: 0.072" total for a primary inductance (Lp) of 320  $\mu\text{H})$

|                                                    |                        |           |                           | AC Line | Input |      |     |           |     |                       |                        |                        |                       |                 |

|----------------------------------------------------|------------------------|-----------|---------------------------|---------|-------|------|-----|-----------|-----|-----------------------|------------------------|------------------------|-----------------------|-----------------|

| Current Harmonic Distortion (% I <sub>fund</sub> ) |                        |           |                           |         |       |      |     | DC Output |     |                       |                        |                        |                       |                 |

| V <sub>rms</sub><br>(V)                            | P <sub>in</sub><br>(W) | PF<br>(-) | l <sub>fund</sub><br>(mA) | THD     | H2    | НЗ   | H5  | H7        | H9  | V <sub>o</sub><br>(V) | ∆V <sub>O</sub><br>(V) | l <sub>o</sub><br>(mA) | P <sub>o</sub><br>(W) | η<br><b>(%)</b> |

| 90                                                 | 88.2                   | 0.991     | 990                       | 8.1     | 0.07  | 5.9  | 4.3 | 1.5       | 1.7 | 181                   | 31.2                   | 440                    | 79.6                  | 90.2            |

| 110                                                | 86.3                   | 0.996     | 782                       | 7.0     | 0.05  | 2.7  | 5.7 | 1.1       | 0.8 | 222                   | 26.4                   | 360                    | 79.9                  | 92.6            |

| 135                                                | 85.2                   | 0.995     | 642                       | 8.2     | 0.03  | 1.5  | 6.8 | 1.1       | 1.5 | 265                   | 20.8                   | 300                    | 79.5                  | 93.3            |

| 180                                                | 87.0                   | 0.994     | 480                       | 9.5     | 0.16  | 4.0  | 6.5 | 3.1       | 4.0 | 360                   | 16.0                   | 225                    | 81.0                  | 93.1            |

| 220                                                | 84.7                   | 0.982     | 385                       | 15      | 0.5   | 8.4  | 7.8 | 5.3       | 1.9 | 379                   | 14.0                   | 210                    | 79.6                  | 94.4            |

| 240                                                | 85.3                   | 0.975     | 359                       | 16.5    | 0.7   | 9.0  | 7.8 | 7.4       | 3.8 | 384                   | 14.0                   | 210                    | 80.6                  | 94.5            |

| 260                                                | 84.0                   | 0.967     | 330                       | 18.8    | 0.7   | 11.0 | 7.0 | 9.0       | 4.0 | 392                   | 13.2                   | 205                    | 80.4                  | 95.7            |

**POWER FACTOR CONTROLLER TEST DATA\***

$^{\ast}$  Measurements performed using Voltech PM1200 ac power analysis.

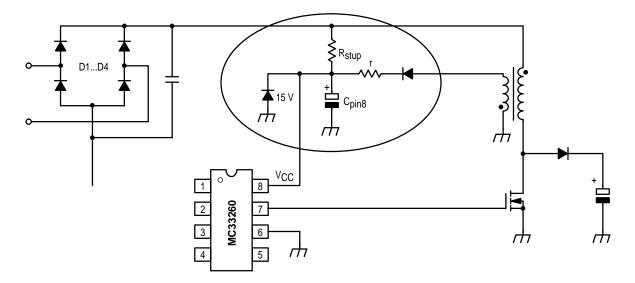

Figure 35. Circuit Supply Voltage

# MC33260 V<sub>CC</sub> SUPPLY VOLTAGE

In some applications, the arrangement shown in Figure 35 must be implemented to supply the circuit. A start–up resistor is connected between the rectified voltage (or one–half wave) to charge the MC33260 V<sub>CC</sub> up to its start–up threshold (11 V typically). The MC33260 turns on and the V<sub>CC</sub> capacitor (C<sub>pin8</sub>) starts to be charged by the PFC transformer auxiliary winding. A resistor, r (in the range of 22  $\Omega$ ) and a 15 V zener should be added to protect the circuit from excessive voltages.

When the PFC preconverter is loaded by an SMPS, the

MC33260 should preferably be supplied by the SMPS itself. In this configuration, the SMPS starts first and the PFC gets active when the MC33260 V<sub>CC</sub> supplied by the power supply, exceeds the device start–up level. With this configuration, the PFC preconverter doesn't require any auxiliary winding and finally a simple coil can be used.

# PCB LAYOUT

The connections of the oscillator and  $V_{\text{Control}}$  capacitors should be as short as possible.

Figure 36. Preconverter loaded by a Flyback SMPS: MC33260 V<sub>CC</sub> Supply

#### **OUTLINE DIMENSIONS**

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights or other. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and with a registered

#### How to reach us:

USA/EUROPE/Locations Not Listed: Motorola Literature Distribution; P.O. Box 5405, Denver, Colorado 80217. 1–303–675–2140 or 1–800–441–2447

#### Customer Focus Center: 1-800-521-6274

JAPAN: Motorola Japan Ltd.; SPD, Strategic Planning Office, 141, 4–32–1 Nishi–Gotanda, Shinagawa–ku, Tokyo, Japan. 81–3–5487–8488

Mfax™: RMFAX0@email.sps.mot.com

- TOUCHTONE 1-602-244-6609

Motorola Fax Back System

- US & Canada ONLY 1-800-774-1848

- http://sps.motorola.com/mfax/

HOME PAGE: http://motorola.com/sps/

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Centre, 2, Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong. 852–26668334

Mfax is a trademark of Motorola, Inc.

$\diamond$